🇨🇳cnBeta (Full RSS)•Freshcollected in 51m

TSMC US Yields Match Taiwan, Tech Transfer

💡TSMC US yield parity secures AI chip supply amid global tensions

⚡ 30-Second TL;DR

What Changed

Arizona factory yields now match Taiwan levels

Why It Matters

Bolsters US semiconductor supply chain resilience for AI chips, mitigating geopolitical risks and ensuring stable production for Nvidia and others.

What To Do Next

Evaluate TSMC N2U process timelines for planning next-gen AI accelerator chip sourcing.

Who should care:Enterprise & Security Teams

🧠 Deep Insight

AI-generated analysis for this event.

🔑 Enhanced Key Takeaways

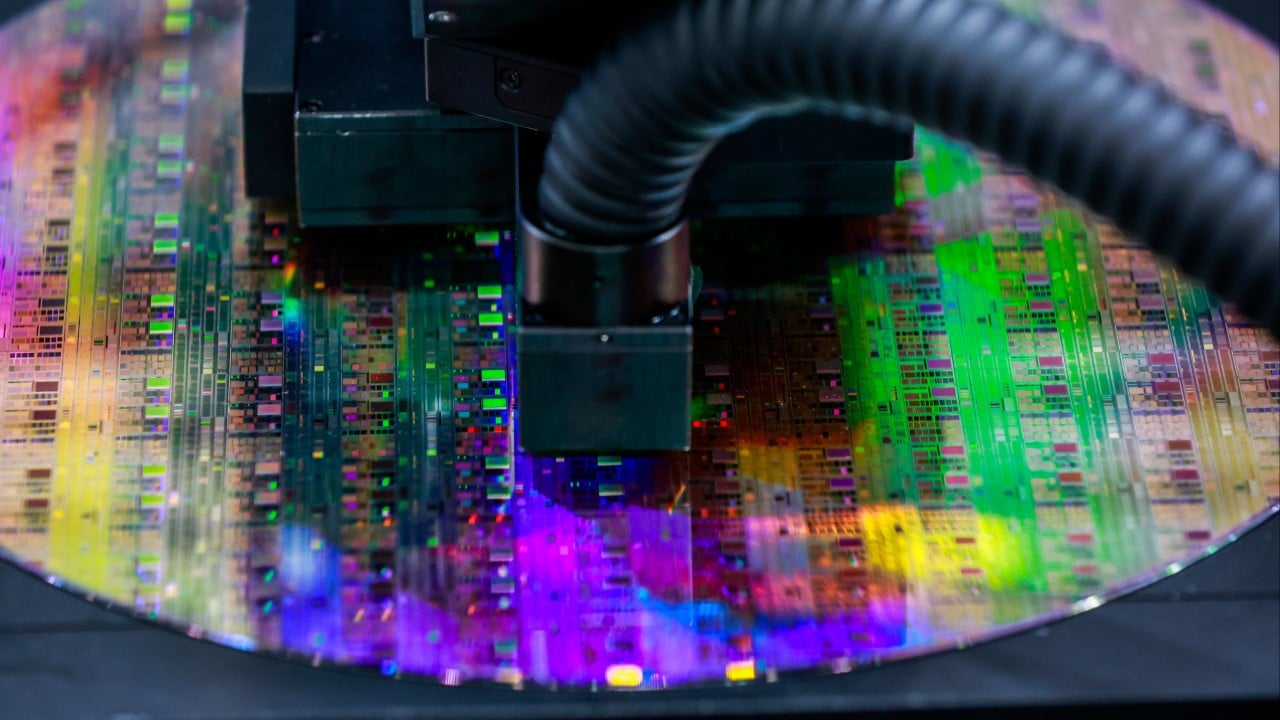

- •The Arizona facility, specifically Fab 21, has successfully transitioned to high-volume production for 4nm (N4) process nodes, which served as the benchmark for achieving yield parity with Taiwan-based fabs.

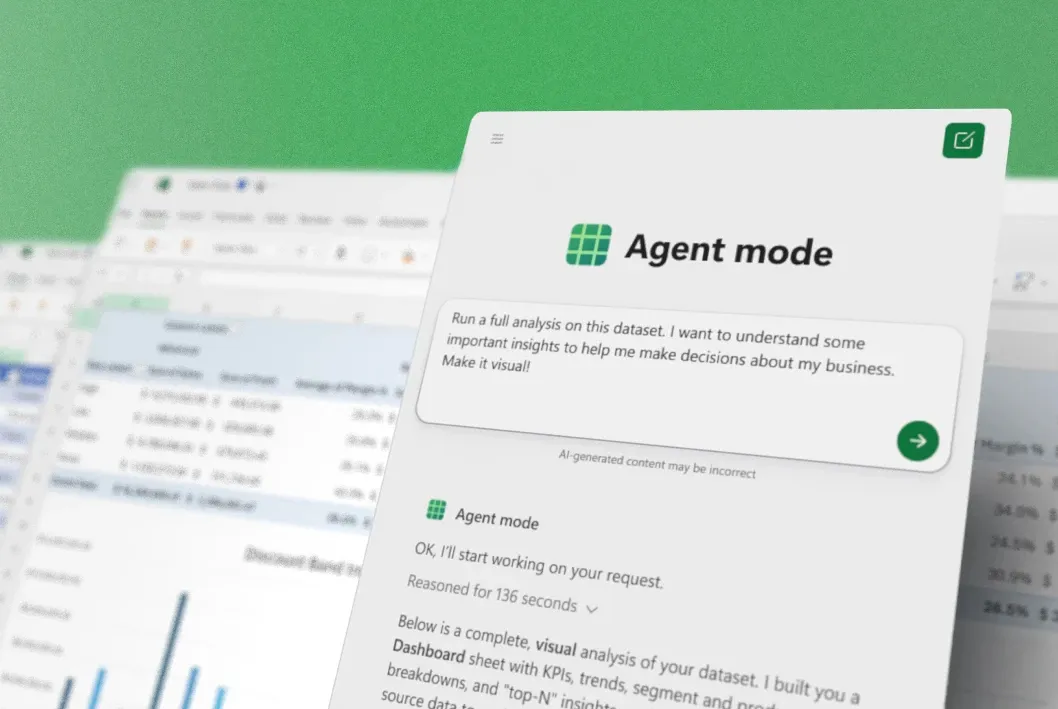

- •The two core technologies being transferred to the US include advanced packaging capabilities (CoWoS) and the integration of TSMC's proprietary 3D IC (System-on-Integrated-Chips) technology to support AI accelerator production locally.

- •Despite yield parity, TSMC continues to navigate significant operational cost differentials, with the company leveraging US CHIPS Act subsidies to offset the higher capital expenditure and labor costs associated with the Arizona expansion.

📊 Competitor Analysis▸ Show

| Feature | TSMC (Arizona) | Intel Foundry | Samsung Foundry |

|---|---|---|---|

| Leading Node | N2 / N2U | 18A / 14A | SF2 / SF2P |

| Packaging | CoWoS / SoIC | Foveros | I-Cube / X-Cube |

| US Capacity | High (Multi-Fab) | High (Internal/External) | Moderate (Texas) |

🛠️ Technical Deep Dive

- A13/A12 Processes: These represent specialized iterations of TSMC's 2nm-class nodes, optimized for high-performance computing (HPC) and mobile efficiency, focusing on backside power delivery networks (BSPDN).

- N2U (N2 Ultra): An enhanced version of the N2 node, specifically designed to provide higher transistor density and improved power-performance-area (PPA) metrics for next-generation AI training chips.

- Yield Parity: Achieved through the deployment of TSMC's 'Golden Recipe' manufacturing protocols, which involve identical lithography tool configurations and automated material handling systems (AMHS) across both Taiwan and Arizona sites.

🔮 Future ImplicationsAI analysis grounded in cited sources

TSMC will prioritize US-based production for major AI hardware partners.

Achieving yield parity in Arizona removes the primary barrier to domestic production for high-margin, high-volume AI accelerator clients.

The Arizona site will become a critical node for US national security chip supply.

The transfer of advanced 3D IC and packaging technologies allows for the complete end-to-end manufacturing of sensitive defense and AI hardware within US borders.

⏳ Timeline

2020-05

TSMC announces intent to build a $12 billion semiconductor facility in Arizona.

2021-04

Construction officially commences on the Arizona site (Fab 21).

2022-12

TSMC announces an expansion to a second fab, increasing total investment to $40 billion.

2024-04

TSMC receives $6.6 billion in direct funding under the US CHIPS and Science Act.

2025-04

TSMC begins initial volume production of 4nm chips at the Arizona facility.

📰

Weekly AI Recap

Read this week's curated digest of top AI events →

👉Related Updates

AI-curated news aggregator. All content rights belong to original publishers.

Original source: cnBeta (Full RSS) ↗