🇨🇳cnBeta (Full RSS)•Stalecollected in 23m

PCIe 8.0 Debuts with 1TB/s Bandwidth

💡1TB/s PCIe 8.0 preps massive bandwidth for AI data centers & HPC

⚡ 30-Second TL;DR

What Changed

PCIe 8.0 first public showcase

Why It Matters

Enables faster AI model training and inference via superior GPU/storage interconnects in data centers. Future-proofs infrastructure for scaling AI workloads amid bandwidth bottlenecks.

What To Do Next

Assess PCIe 8.0 specs for upcoming AI cluster GPU interconnect planning.

Who should care:Enterprise & Security Teams

🧠 Deep Insight

Web-grounded analysis with 5 cited sources.

🔑 Enhanced Key Takeaways

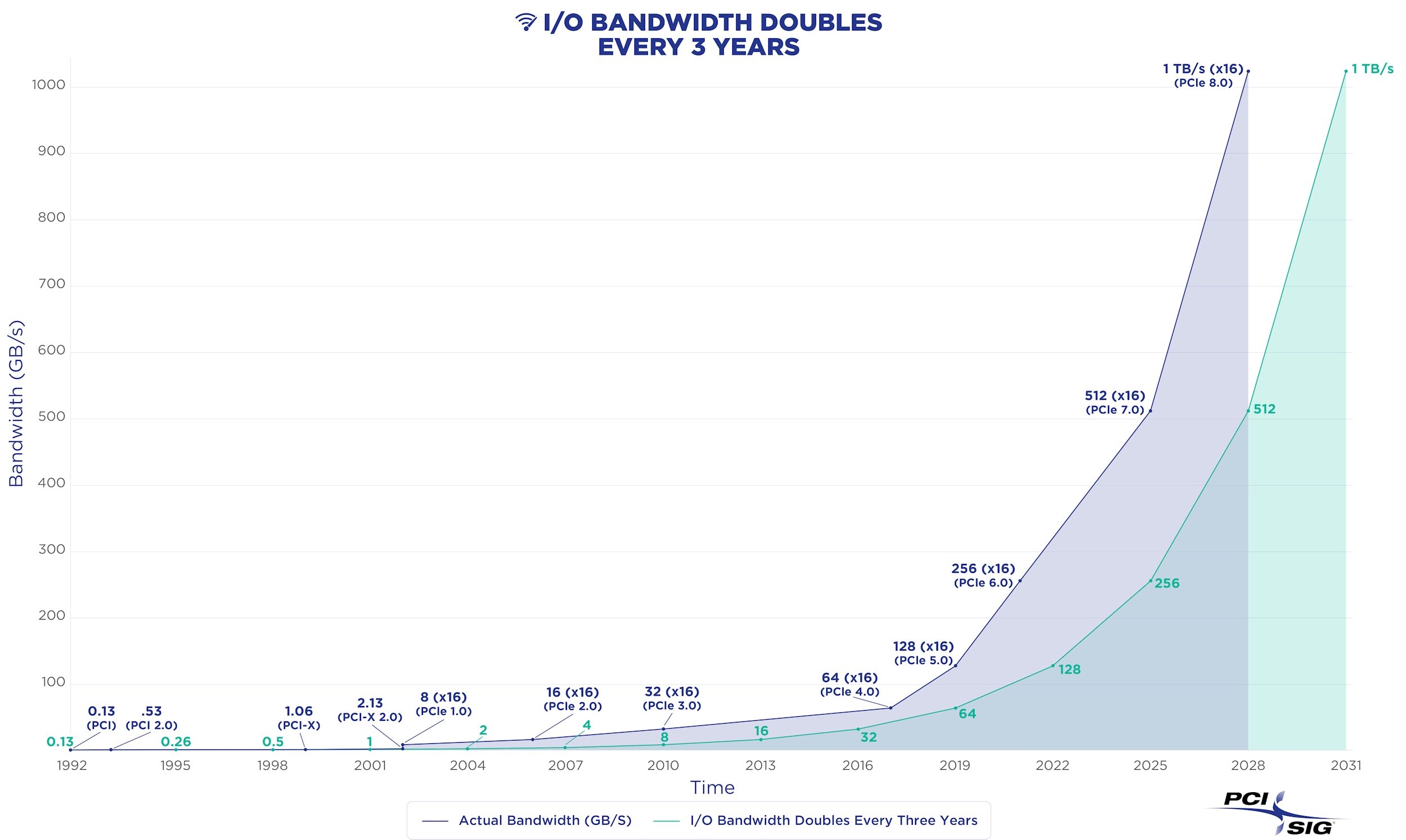

- •PCIe 8.0 doubles PCIe 7.0's raw bit rate to 256 GT/s per lane using PAM4 signaling, forward error correction (FEC), and Flit Mode encoding.[1][3]

- •PCI-SIG has released Draft 0.3 of the PCIe 8.0 specification to members, which reviews new connector technology for improved signal integrity.[3][5]

- •Marvell demonstrated a PCIe 8.0 SerDes at 256 GT/s at DesignCon 2026, targeting low-power, low-latency transmission for AI data centers.[4]

🛠️ Technical Deep Dive

- •Raw bit rate: 256.0 GT/s per lane, doubling PCIe 7.0's 128 GT/s.[1][3]

- •Signaling: Continues PAM4 with forward error correction (FEC) and Flit Mode encoding from PCIe 6.0/7.0.[1]

- •Bandwidth: Up to 1.0 TB/s bi-directional in x16 configuration.[1][3][4]

- •Protocol enhancements: Improve real-world bandwidth and reduce power consumption.[1]

- •New features under review: Potential new connector technology for better signal integrity.[5]

🔮 Future ImplicationsAI analysis grounded in cited sources

PCIe 8.0 finalization expected by 2028

Backward compatibility maintained with prior generations

PCIe 8.0 will support older PCIe 4.0/5.0 devices on new motherboards and vice versa at reduced speeds, easing upgrades.[2]

⏳ Timeline

2010-11

PCIe 3.0 released at 8 GT/s

2017-06

PCIe 4.0 released at 16 GT/s

2019-05

PCIe 5.0 released at 32 GT/s

2022-01

PCIe 6.0 released at 64 GT/s

2025-12

PCIe 7.0 specification released at 128 GT/s

2026-02

PCI-SIG releases PCIe 8.0 Draft 0.3 and Marvell demos SerDes at DesignCon

📎 Sources (5)

Factual claims are grounded in the sources below. Forward-looking analysis is AI-generated interpretation.

- Tom's Hardware — Pci Sig Announces Pcie 8 0 Spec with Twice the Bandwidth 1tb S of Peak Bandwidth 256 Gt S Per Lane and a Possible New Connector

- darkflash.com — What Is Pcie 8 Explained

- pcisig.com — Pcier 80 Specification Draft 03 Now Available Members

- marvell.com — Marvell Pcie8 Serdes Demo Designcon2026

- pcisig.com — Pcie 80 Specification Version 03 Now Available Members

📰

Weekly AI Recap

Read this week's curated digest of top AI events →

👉Related Updates

AI-curated news aggregator. All content rights belong to original publishers.

Original source: cnBeta (Full RSS) ↗