🇨🇳cnBeta (Full RSS)•Stalecollected in 16h

TSMC Scales Arizona to 12 Fabs at $165B

💡TSMC's $165B US expansion secures AI chip supply chain resilience.

⚡ 30-Second TL;DR

What Changed

12 factories planned: 8 wafer fabs + 4 advanced packaging plants

Why It Matters

Boosts US chip production capacity critical for AI GPUs and accelerators, enhancing supply chain security amid geopolitical risks. Supports scaling of AI infrastructure domestically.

What To Do Next

Review TSMC supplier portal for Arizona fab certification timelines to plan AI hardware procurement.

Who should care:Enterprise & Security Teams

🧠 Deep Insight

AI-generated analysis for this event.

🔑 Enhanced Key Takeaways

- •The expansion is heavily supported by the U.S. CHIPS and Science Act, with TSMC securing significant direct funding and investment tax credits to offset the higher operational costs of U.S.-based manufacturing compared to Taiwan.

- •The 12-fab complex is designed to create a comprehensive 'silicon ecosystem' in Arizona, aiming to attract key supply chain partners, including chemical suppliers and equipment manufacturers, to localize production.

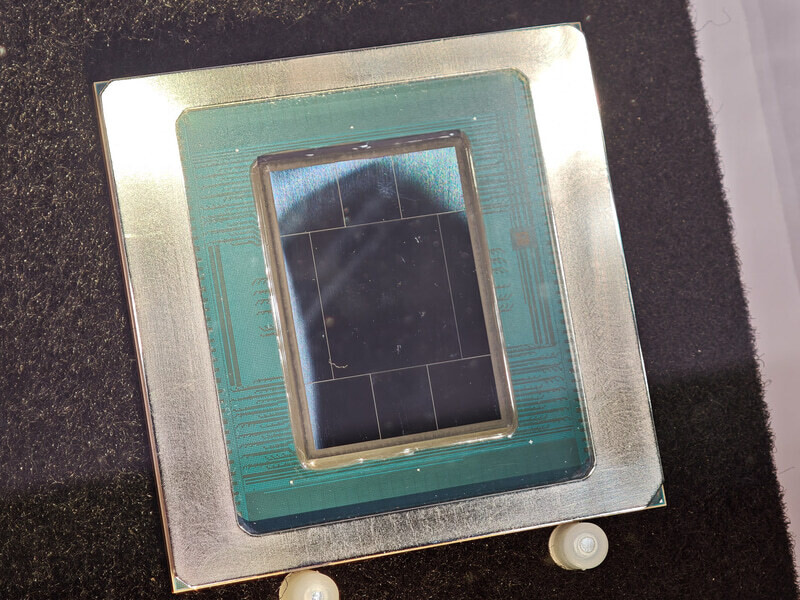

- •The advanced packaging facilities are critical for supporting the 'CoWoS' (Chip-on-Wafer-on-Substrate) technology, which is in high demand for AI accelerators and high-performance computing (HPC) chips.

📊 Competitor Analysis▸ Show

| Feature | TSMC (Arizona) | Intel (Foundry) | Samsung (Foundry) |

|---|---|---|---|

| Primary Node Focus | 2nm / 1.6nm (A16) | 18A / 14A | 2nm / 1.4nm |

| Advanced Packaging | CoWoS / SoIC | Foveros | I-Cube / H-Cube |

| U.S. Manufacturing | Massive scale (12 fabs) | Established (Ohio/AZ) | Expanding (Texas) |

| Market Strategy | Pure-play foundry | IDM 2.0 | Integrated Foundry |

🛠️ Technical Deep Dive

- Node Roadmap: The Arizona site is slated to produce chips on the N4, N3, and eventually N2 (2nm) and A16 (1.6nm) process nodes.

- Advanced Packaging: Integration of CoWoS (Chip-on-Wafer-on-Substrate) and SoIC (System-on-Integrated-Chips) to enable 3D stacking of logic and HBM (High Bandwidth Memory).

- EUV Utilization: High-NA EUV lithography machines are expected to be deployed in the later-stage fabs to support sub-2nm manufacturing requirements.

🔮 Future ImplicationsAI analysis grounded in cited sources

TSMC Arizona will become the largest foreign-owned semiconductor manufacturing hub in the United States.

The scale of 12 fabs exceeds the footprint of any other foreign semiconductor investment currently operating or planned in the U.S.

The expansion will significantly reduce TSMC's reliance on Taiwan for high-end AI chip production.

By localizing 2nm and advanced packaging capacity in the U.S., TSMC provides a domestic supply chain alternative for major U.S. hyperscalers.

⏳ Timeline

2020-05

TSMC announces intent to build a $12 billion fab in Arizona.

2022-12

TSMC increases investment to $40 billion and announces a second fab.

2024-04

TSMC receives $6.6 billion in CHIPS Act grants and announces a third fab, raising total investment to $65 billion.

📰

Weekly AI Recap

Read this week's curated digest of top AI events →

👉Related Updates

AI-curated news aggregator. All content rights belong to original publishers.

Original source: cnBeta (Full RSS) ↗