🇨🇳cnBeta (Full RSS)•Stalecollected in 21m

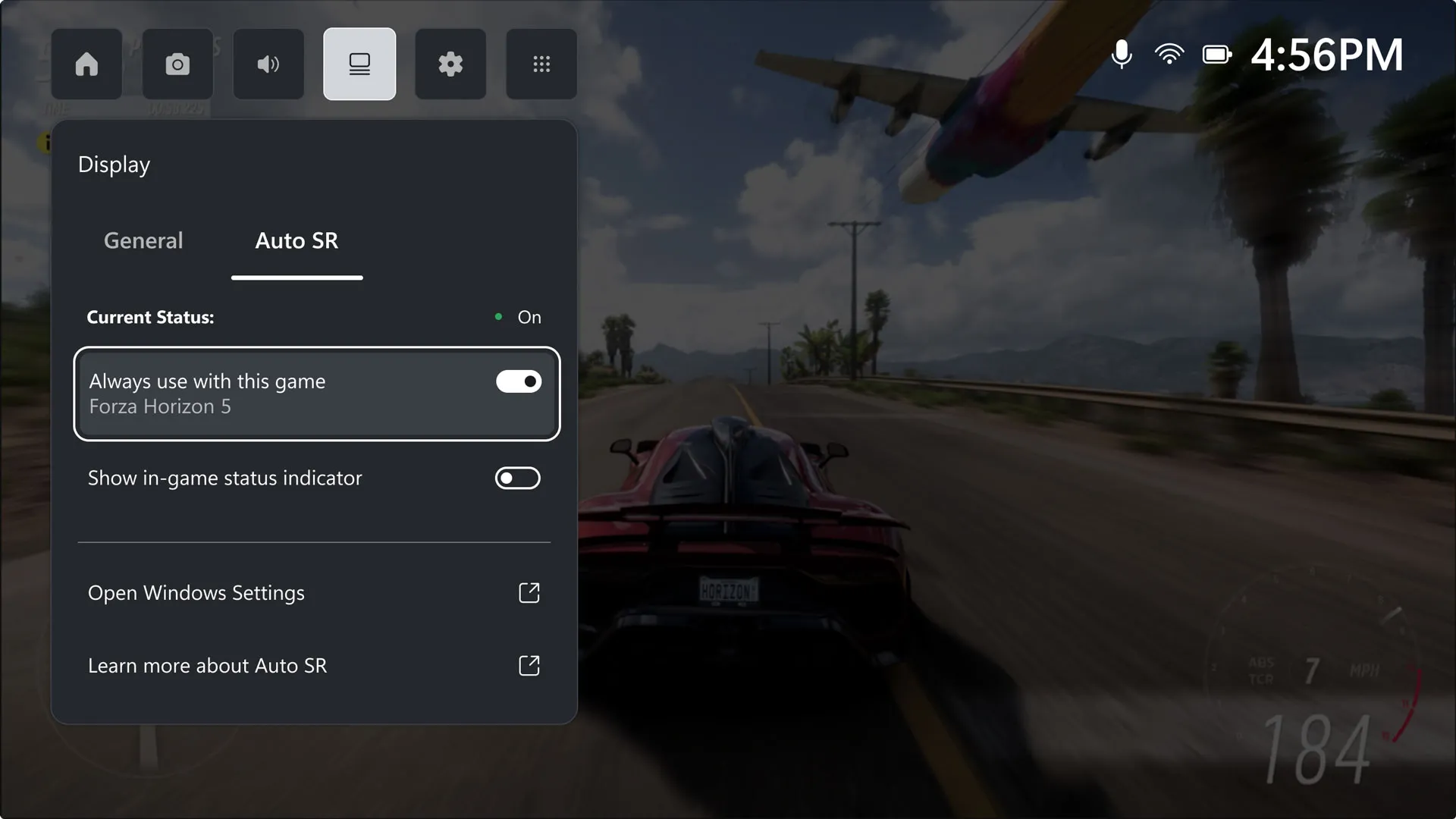

TSMC 3nm Capacity Tight for Non-Loyal Customers

💡TSMC 3nm crunch favors loyalists—scramble for AI chip supply priority.

⚡ 30-Second TL;DR

What Changed

AI boom causes explosive demand for TSMC 3nm process.

Why It Matters

Supply limits disadvantage new entrants in AI hardware, benefiting established players like Nvidia, potentially slowing industry-wide AI chip innovation.

What To Do Next

Assess Samsung or Intel Foundry alternatives if lacking TSMC long-term status for AI chip production.

Who should care:Enterprise & Security Teams

🧠 Deep Insight

AI-generated analysis for this event.

🔑 Enhanced Key Takeaways

- •TSMC's N3P (3nm enhanced) process node has become the primary driver for high-performance computing (HPC) and AI accelerator demand, leading to a significant shift in wafer allocation strategies toward strategic partners like Apple, NVIDIA, and AMD.

- •The capacity crunch is exacerbated by the transition of major cloud service providers (CSPs) to custom-designed AI silicon, which competes directly with traditional fabless chipmakers for limited 3nm production slots.

- •TSMC has reportedly implemented a 'value-based' pricing model for 3nm capacity, where non-loyal or short-term customers face significant premiums or are deprioritized in favor of long-term capacity reservation agreements.

📊 Competitor Analysis▸ Show

| Feature | TSMC (3nm/N3P) | Samsung Foundry (3nm/SF3) | Intel Foundry (18A) |

|---|---|---|---|

| Maturity | High (Mass Production) | Moderate (Early Production) | Emerging (Ramping) |

| Yield | Industry Leading | Improving | Developing |

| Primary Focus | HPC/AI/Mobile | Mobile/HPC | HPC/Internal/Foundry |

🛠️ Technical Deep Dive

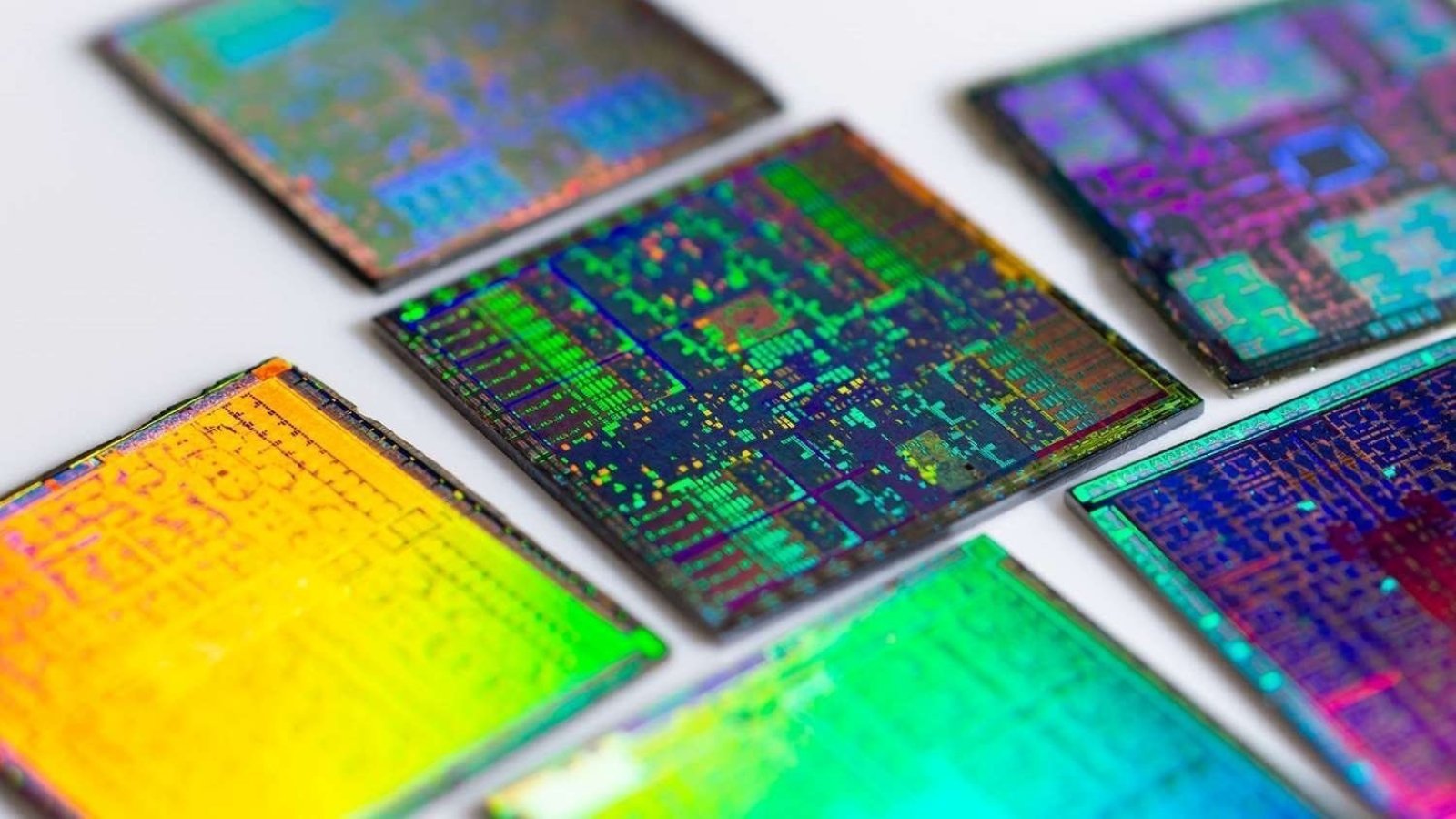

- •TSMC 3nm family utilizes FinFlex technology, allowing designers to mix and match standard cells within the same block to optimize for power, performance, and area (PPA).

- •N3P process node offers approximately 5% speed improvement, 5-10% power reduction, and 1.04x density improvement compared to the base N3E node.

- •The process employs extreme ultraviolet (EUV) lithography with high-NA EUV tools being integrated into subsequent iterations to manage complex patterning requirements for sub-3nm features.

🔮 Future ImplicationsAI analysis grounded in cited sources

Increased vertical integration among AI hyperscalers.

Capacity constraints will force major cloud providers to invest directly in long-term foundry partnerships or co-development to guarantee supply for custom AI silicon.

Widening performance gap between top-tier and mid-tier AI hardware.

Limited access to leading-edge 3nm nodes will restrict smaller AI chip startups from achieving the power efficiency and compute density required to compete with industry leaders.

⏳ Timeline

2022-12

TSMC officially begins volume production of 3nm (N3) process technology.

2023-09

TSMC introduces N3E, an enhanced 3nm process, to improve yield and performance.

2024-06

TSMC announces N3P, further optimizing the 3nm family for high-performance computing.

2025-04

TSMC reports record-high utilization rates for 3nm capacity driven by AI demand.

📰

Weekly AI Recap

Read this week's curated digest of top AI events →

👉Related Updates

AI-curated news aggregator. All content rights belong to original publishers.

Original source: cnBeta (Full RSS) ↗