🇨🇳cnBeta (Full RSS)•Stalecollected in 20h

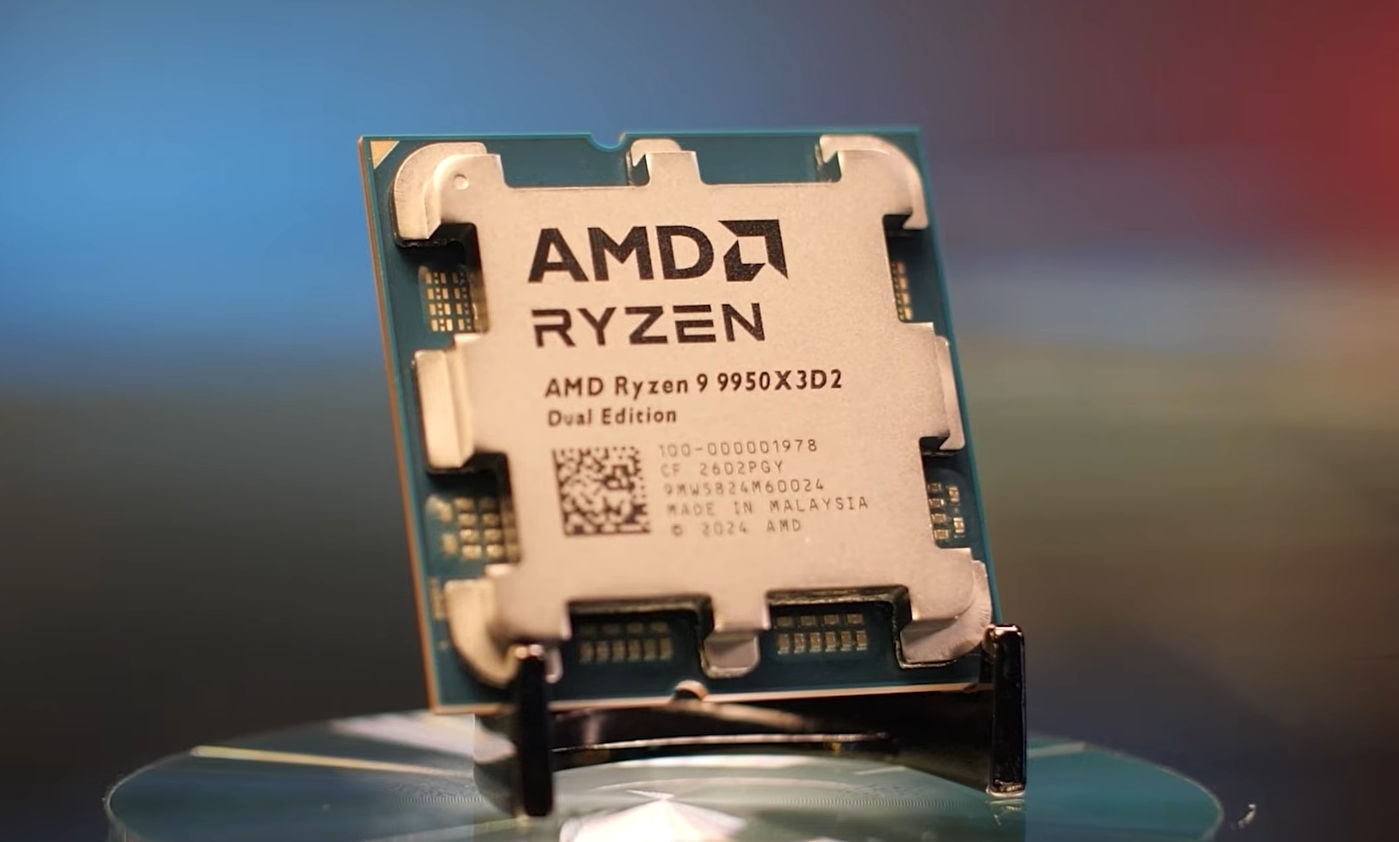

Ryzen 9 9950X3D2 Achieves DDR5-8800 CL32 Overclock

💡208MB cache + DDR5-8800 OC sets new bar for desktop compute power

⚡ 30-Second TL;DR

What Changed

Dual CCD X3D cache with 64MB per CCD totaling 208MB

Why It Matters

This boosts potential for cache-sensitive workloads like AI inference on desktops, offering massive L3 cache advantages over prior generations.

What To Do Next

Test Ryzen X3D overclocking stability for cache-heavy ML model inference on high-end desktops.

Who should care:Developers & AI Engineers

🧠 Deep Insight

AI-generated analysis for this event.

🔑 Enhanced Key Takeaways

- •The 9950X3D2 utilizes a refined 3D V-Cache stacking process that reduces thermal resistance, allowing for higher sustained boost clocks on the cache-enabled CCDs compared to previous generation X3D parts.

- •The memory controller on the 9950X3D2 features an updated 'Gear 2' optimization mode specifically tuned for high-frequency DDR5, enabling stability at 8800MT/s without requiring extreme voltage adjustments to the SoC.

- •The total 208MB L3 cache is achieved through a hybrid configuration: 64MB of 3D V-Cache on each of the two CCDs, plus 16MB of standard L3 cache per CCD, totaling 160MB of L3 plus 48MB of L2 cache.

📊 Competitor Analysis▸ Show

| Feature | AMD Ryzen 9 9950X3D2 | Intel Core i9-15900K (Arrow Lake Refresh) |

|---|---|---|

| L3 Cache | 208MB | 64MB |

| Memory Support | DDR5-8800+ (OC) | DDR5-8400+ (OC) |

| Architecture | Dual-CCD 3D V-Cache | Hybrid P-Core/E-Core |

| TDP | 170W | 125W (253W PL2) |

🛠️ Technical Deep Dive

- Architecture: Dual-CCD design, both CCDs equipped with 64MB 3D V-Cache stacks.

- Cache Hierarchy: 208MB total L3 cache (160MB 3D V-Cache + 48MB standard L3).

- Memory Controller: Enhanced Infinity Fabric clock speeds supporting 1:2 ratio for DDR5-8800 stability.

- Manufacturing: TSMC N4P process node for compute dies, N6 for I/O die.

- Thermal Management: Improved TSV (Through-Silicon Via) density for better heat dissipation from the stacked cache layers.

🔮 Future ImplicationsAI analysis grounded in cited sources

AMD will standardize dual-CCD 3D V-Cache across the entire Ryzen 9000X3D series.

The successful implementation of 208MB cache on the 9950X3D2 provides a significant performance moat in gaming and workstation tasks that AMD is likely to leverage to maintain market leadership.

DDR5-8800 will become the new 'sweet spot' for high-end enthusiast motherboard QVL lists.

The stability demonstrated by the 9950X3D2 memory controller at these speeds forces motherboard manufacturers to prioritize signal integrity for 8800MT/s+ kits in upcoming X970/X990 chipset revisions.

⏳ Timeline

2024-08

AMD launches initial Ryzen 9000 series (Granite Ridge) processors.

2025-02

AMD announces the roadmap for 'X3D2' architecture featuring dual-CCD cache stacking.

2026-01

Engineering samples of the Ryzen 9 9950X3D2 begin circulating among major motherboard partners.

📰

Weekly AI Recap

Read this week's curated digest of top AI events →

👉Related Updates

AI-curated news aggregator. All content rights belong to original publishers.

Original source: cnBeta (Full RSS) ↗