🇨🇳cnBeta (Full RSS)•Freshcollected in 28m

JEDEC Speeds Up DDR6 for 2028 Launch

💡DDR6 advances fast—key for AI data center memory upgrades by 2028 (impacts GPU/TPU scaling)

⚡ 30-Second TL;DR

What Changed

JEDEC leads collaborative DDR6 standardization efforts

Why It Matters

DDR6 will boost memory bandwidth for AI training and inference in data centers, enabling larger models on future servers.

What To Do Next

Track JEDEC DDR6 spec releases to evaluate compatibility for next-gen AI server builds.

Who should care:Enterprise & Security Teams

🧠 Deep Insight

AI-generated analysis for this event.

🔑 Enhanced Key Takeaways

- •DDR6 is expected to feature a significant leap in data rates, with initial specifications targeting 8.8 Gbps to 17.6 Gbps, and potential future scaling up to 21 Gbps.

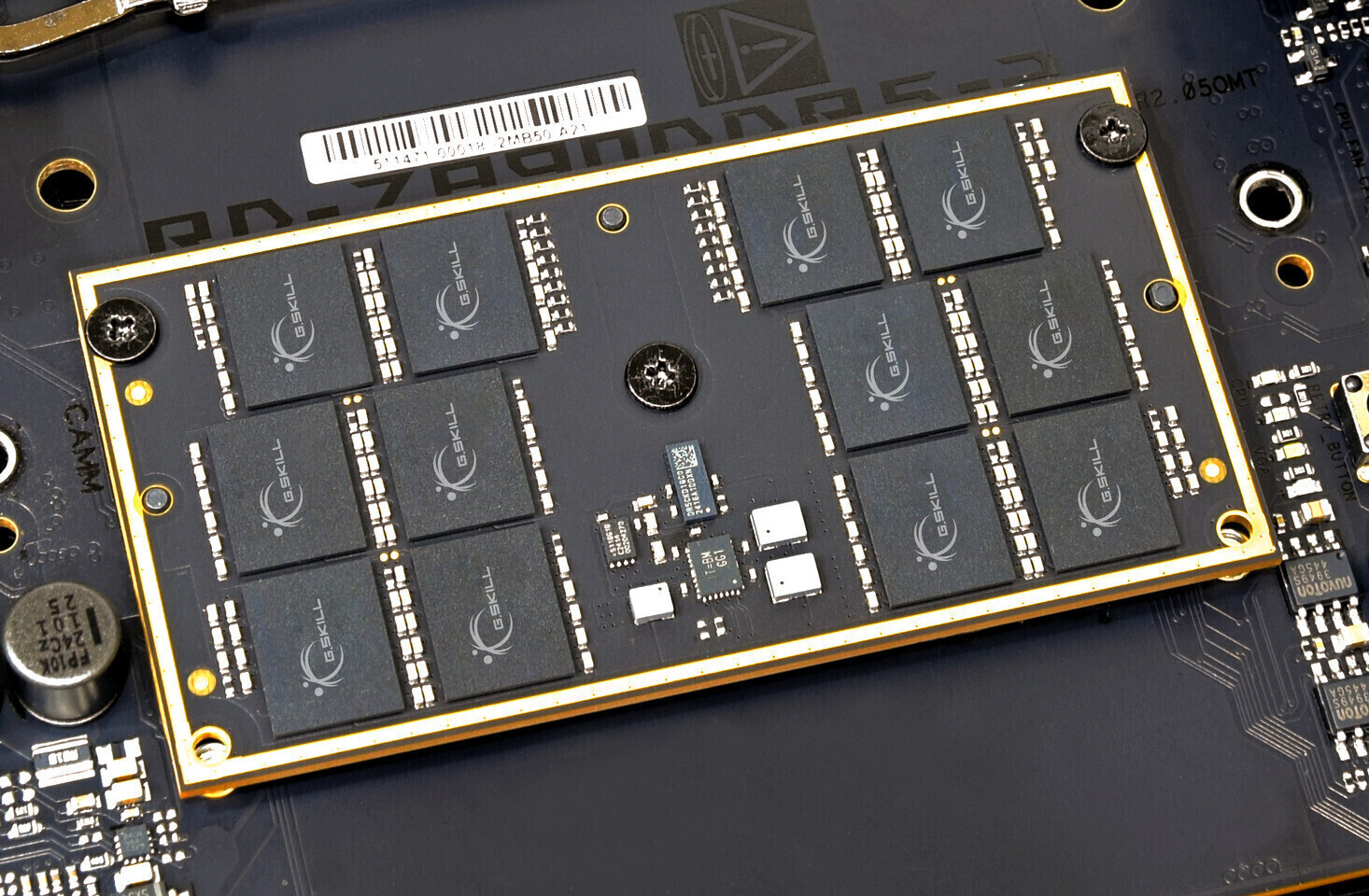

- •The standard is designed to utilize a new dual-channel DIMM architecture per module, which aims to improve memory efficiency and bandwidth utilization compared to the single-channel approach of DDR5.

- •JEDEC is focusing on integrating advanced power management features directly onto the memory modules to address the thermal and power delivery challenges posed by the increased operating frequencies.

🛠️ Technical Deep Dive

- •Targeted data rates: Initial specifications range from 8.8 Gbps to 17.6 Gbps, with potential for further scaling.

- •Architecture: Transition to a dual-channel DIMM design per module to enhance bandwidth and efficiency.

- •Power Management: Enhanced on-module Power Management Integrated Circuit (PMIC) designs to handle higher power density and thermal requirements.

- •Signal Integrity: Implementation of advanced equalization techniques to maintain signal quality at significantly higher clock speeds.

🔮 Future ImplicationsAI analysis grounded in cited sources

DDR6 will necessitate a complete redesign of motherboard memory trace layouts.

The shift to higher data rates and dual-channel DIMM architectures requires stricter signal integrity standards and altered physical routing on PCBs.

Memory power consumption will become a primary bottleneck for high-performance computing systems.

The increased frequency and bandwidth requirements of DDR6 will drive higher power draw, necessitating more sophisticated cooling solutions for memory modules.

⏳ Timeline

2020-07

JEDEC officially releases the DDR5 SDRAM standard (JESD79-5).

2022-02

JEDEC announces the formation of committees to begin preliminary discussions on next-generation memory standards beyond DDR5.

2024-01

Industry reports confirm JEDEC has accelerated the development timeline for DDR6 to meet rising AI and server workload demands.

📰

Weekly AI Recap

Read this week's curated digest of top AI events →

👉Related Updates

AI-curated news aggregator. All content rights belong to original publishers.

Original source: cnBeta (Full RSS) ↗