🇨🇳cnBeta (Full RSS)•Recentcollected in 35m

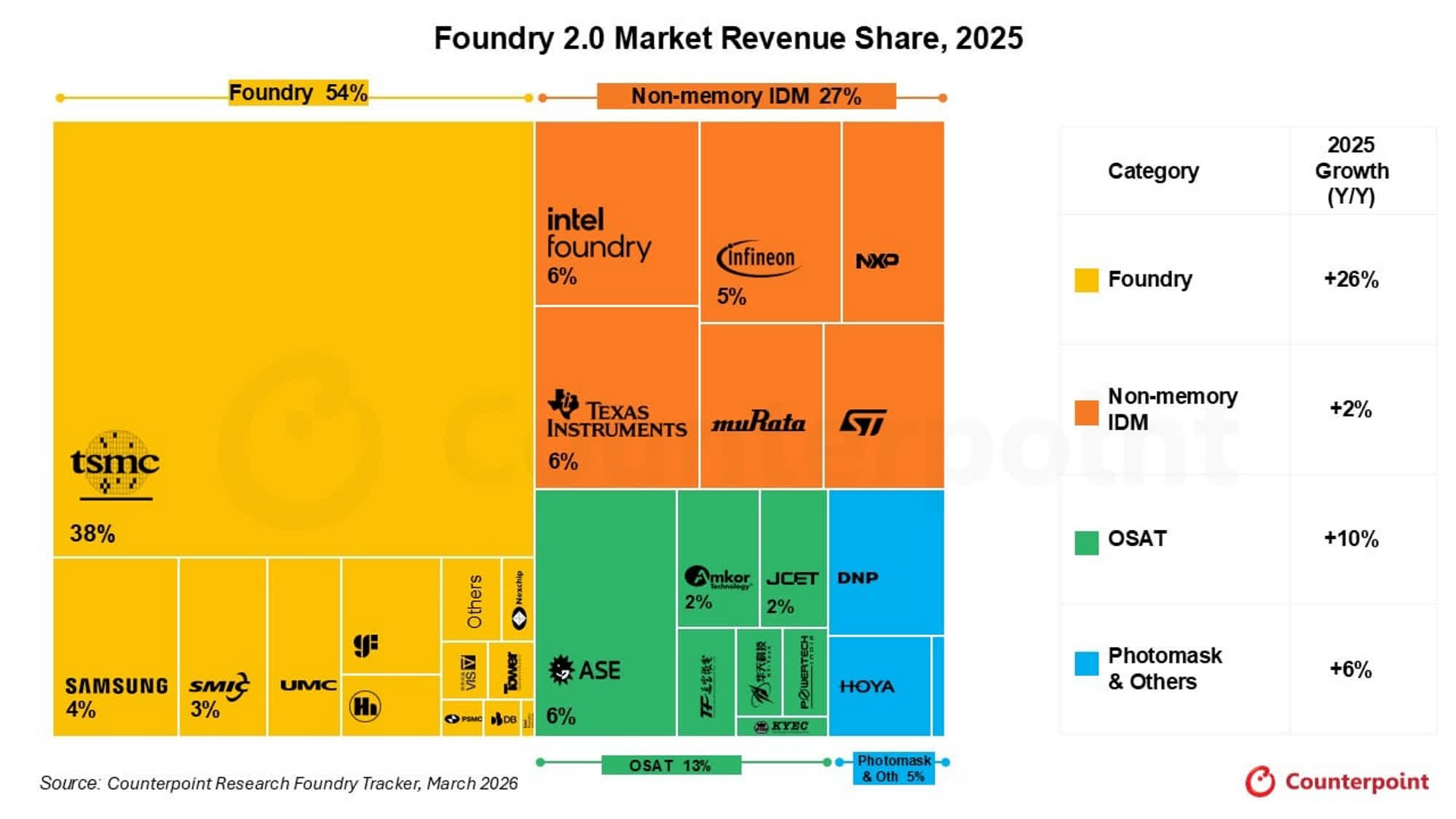

2025 Foundry Hits $320B on AI Surge

💡AI fuels $320B foundry boom—key for AI chip procurement strategy

⚡ 30-Second TL;DR

What Changed

2025 revenue reaches $320B, +16% YoY record high

Why It Matters

Signals robust AI hardware supply growth, easing chip shortages for AI training/inference. Boosts confidence in scaling AI infrastructure investments.

What To Do Next

Review Counterpoint's full Foundry 2.0 report for AI chip supply forecasts.

Who should care:Founders & Product Leaders

🧠 Deep Insight

AI-generated analysis for this event.

🔑 Enhanced Key Takeaways

- •The 'Foundry 2.0' framework emphasizes the shift from traditional wafer manufacturing to a comprehensive service model that integrates advanced packaging (CoWoS), silicon photonics, and heterogeneous chiplet integration.

- •Geopolitical diversification is a major component of the 2025 revenue surge, as foundries aggressively expanded capacity in the US, Japan, and Germany to mitigate supply chain risks associated with concentration in Taiwan.

- •The 16% YoY growth is heavily skewed toward sub-7nm process nodes, with 3nm and 2nm production capacity becoming the primary bottleneck and pricing premium driver for AI-focused hyperscalers.

📊 Competitor Analysis▸ Show

| Feature | TSMC | Samsung Foundry | Intel Foundry |

|---|---|---|---|

| Leading Node | 2nm (N2) | 2nm (SF2) | 18A |

| Advanced Packaging | CoWoS / SoIC | I-Cube / H-Cube | Foveros |

| AI Market Focus | High-performance GPU/ASIC | HBM-integrated logic | High-performance CPU/AI |

🛠️ Technical Deep Dive

- Shift to Gate-All-Around (GAA) transistor architectures at 2nm nodes to improve power efficiency and performance density for AI workloads.

- Adoption of backside power delivery networks (BSPDN) to reduce IR drop and signal interference in high-frequency AI accelerators.

- Expansion of Chip-on-Wafer-on-Substrate (CoWoS) capacity to address the critical HBM (High Bandwidth Memory) integration bottleneck for generative AI training chips.

🔮 Future ImplicationsAI analysis grounded in cited sources

Foundry capital expenditure will shift from pure lithography to advanced packaging infrastructure by 2027.

The physical limitations of monolithic die scaling necessitate multi-die chiplet architectures, making packaging the new primary performance bottleneck.

Regional foundry pricing will diverge significantly based on local subsidy structures.

The high operational costs of non-Taiwanese fabs are forcing foundries to pass on localized manufacturing premiums to customers seeking supply chain resilience.

⏳ Timeline

2022-12

TSMC begins mass production of 3nm (N3) process technology.

2023-08

TSMC announces massive expansion of CoWoS packaging capacity to meet surging AI demand.

2024-04

TSMC receives $6.6 billion in CHIPS Act funding for US-based advanced manufacturing.

2025-02

Foundry industry reports record-breaking quarterly revenue driven by AI accelerator shipments.

📰

Weekly AI Recap

Read this week's curated digest of top AI events →

👉Related Updates

AI-curated news aggregator. All content rights belong to original publishers.

Original source: cnBeta (Full RSS) ↗